How Do Phase-Locked Loops Synchronize Timing in LCD Systems?

A phase-locked loop (PLL) is an electronic feedback circuit that locks an output clock to a reference signal.

A phase-locked loop (PLL) is an electronic feedback circuit that locks an output clock to a reference signal.

LCD power consumption in an embedded system can be reduced by turning the screen off when possible and dimming the backlight.

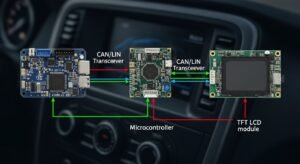

In automotive systems, a microcontroller handles CAN or LIN bus integration with LCD modules by acting as a bus node.

Crosstalk in LCDs occurs when signals interfere between adjacent pixels, leading to ghosting or blurring.

Multiplexing in LCDs reduces pin count to simplify hardware design. It lowers manufacturing costs for small and medium size LCDs.

DMA enables direct memory access to move frame buffer data to LCD modules without CPU involvement. This speeds up display updates for embedded systems.

Developers create a dedicated LCD update task to manage graphic LCD module rendering. This task uses xTaskCreate for real-time operating systems.

Addressing modes are a basic idea in computer architecture, and they shape how microcontrollers and software handle display memory.

CRI (Color Rendering Index) measures how accurately a light source shows colors compared to natural daylight, on a scale from 0 (poor accuracy) to 100 (perfect accuracy).

To show right-to-left (RTL) text on LCD screens like those with the AIP31066 controller, you set the “Entry Mode Set” command with the cursor direction bit (ID) to 0.

Download our comprehensive catalog to explore 10,000+ LCD module options in detail:

0.42-10.11 inch TFT LCD

16×2-320×240 COB LCD

8×2-320×240 COG LCD