Every digital product—no matter how small—relies on moving bits from one place to another. The question that often decides cost, performance, and reliability is simple: should I push those bits in parallel or in serial? This guide draws on my 13-year career designing liquid-crystal display modules to explain where each method shines, where it fails, and how upcoming standards like USB4 and PCIe 6.0 will reshape engineering choices for years to come.

Foundational Concepts

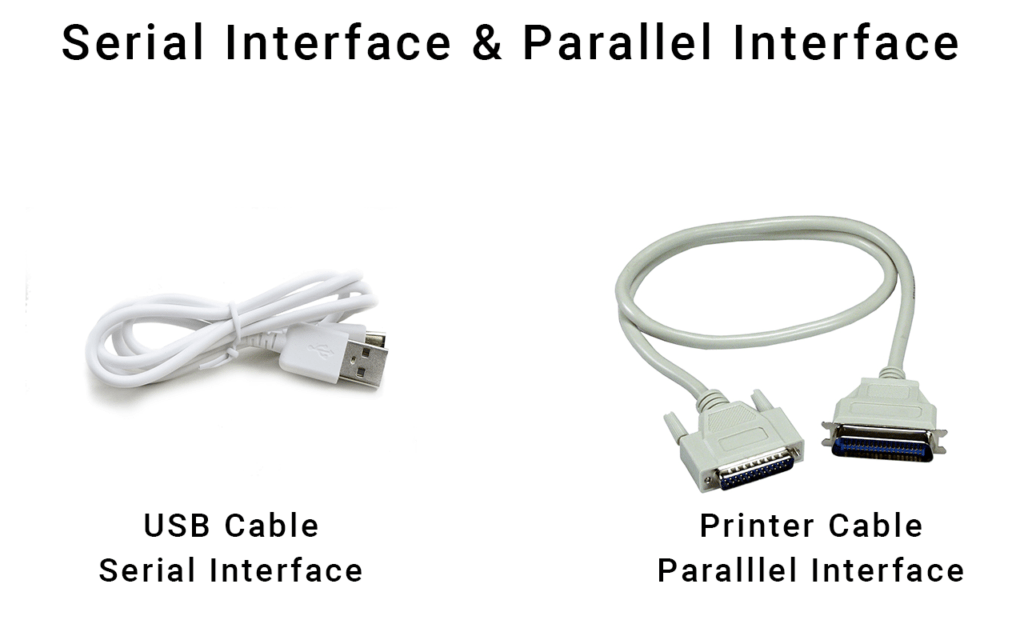

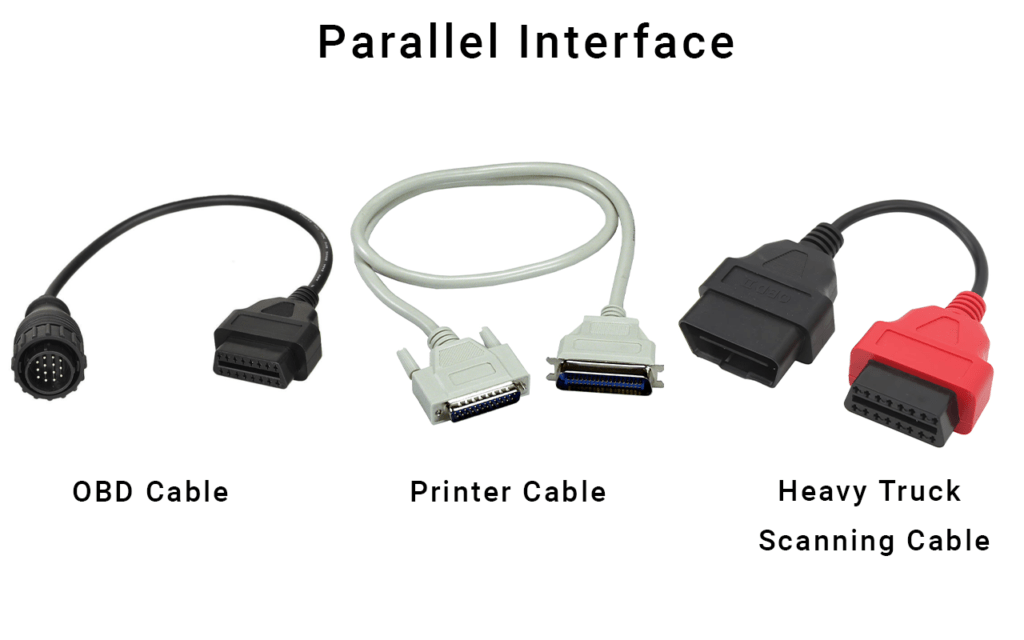

A parallel link pushes many bits at the same moment across independent conductors. By contrast, a serial link pushes bits one after another down a far smaller set of wires. Conceptually simple—but each choice carries deep consequences for distance, noise, power, and cost(How Can a Serial In and Parallel Out Shift Register Simplify MCU to LCD Communication?).

| Feature | Serial Link | Parallel Link |

|---|---|---|

| Data lines | 1–4 typical | 8–64 typical |

| Raw throughput per clock | 1bit | ≥8bits |

| Clock skew issues | Negligible | Significant beyond 0.3 m-traces |

| EMI/crosstalk risk | Low | High on long cables |

| Typical distance | >10m with twisted pair |

Serial sends bits one by one over a minimal conductor count, often with differential signaling to cancel common-mode noise. Parallel transmits many bits simultaneously, trading more copper for raw width and historically simpler silicon interfaces.

Key Physical Principles

- Differential pairs double noise headroom by using opposite-phase signals on matched traces(Comprehensive Guide to LCD Interface Modes).

- Clock skew in parallel buses grows with trace length, making timing closure difficult past a few hundred megahertz.

| Interface | Type | Max Practical Bandwidth | Primary Deployment |

|---|---|---|---|

| RS-232 | Serial | 115.2kbps | Point-to-point control links |

| I²C | Serial | 5Mbps | On-board sensors |

| SPI | Serial | 100Mbps typical | Flash memories, displays |

| DDR4 | Parallel | 25.6GB/s per channel | CPU-RAM links |

| PCI | Parallel | 133MB/s | Legacy expansion slots |

| SATA | Serial | 6Gbps | Storage drives |

When Should You Choose Serial Over Parallel Communication?

Serial excels when distance, noise, or connector cost dominates the design problem. In one industrial LCD kiosk, I once cut harness cost by 37% simply by swapping a 24-bit RGB parallel cable for a single-pair LVDS serial stream.

Use serial for long runs, differential noise immunity, flexible connector pinouts, and compliance with modern plug-and-play buses.

Copper pairs carrying 3Gbps serial Ethernet maintain eye margins over 100m; a comparable 32-wire parallel ribbon would collapse under skew and crosstalk at 0.5m.

When Does Parallel Communication Still Make Sense?

Parallel wins inside tightly-coupled systems where traces are short, noise is controlled, and latency matters more than aggregate gigabits(What EMI/EMC Rules Must Automotive LCD Displays Follow?).

Keep parallel on-board for memory buses or wide-pixel LCD panels when line-lengths are under 5cm and synchronous strobe already exists.

Memory throughput vs. serialization delay

Switching a microcontroller’s 8-bit SDRAM bus to serial QSPI reduces pin area but introduces 4-cycle FIFO latency—unacceptable for real-time frame buffers in some HMI designs(How Are Embedded LCDs Used in Human-Machine Interfaces (HMIs) for Industrial Control Systems?).

Predictable timing

In stepper-motor drive boards, parallel GPIO pulses achieve nanosecond-level determinism without SerDes tails, critical for micro-stepping accuracy at 80kHz.

| Parallel Edge | Design Context | Why Serial Falls Short |

|---|---|---|

| Zero serialization latency | Real-time control loops | SerDes adds pipeline |

| Clock already present | Synchronous DDR RAM | Serial would duplicate clock |

| Ultra-low protocol overhead | ASIC internal buses | Packet framing wastes gates |

Serial vs Parallel inside Embedded Systems

Embedded engineers juggle UART, SPI, I²C, and more. Each protocol maps onto the broader serial-parallel spectrum(How to Implement UART for Monochrome LCD Communication?).

For sensors, SPI or I²C cover 90% of needs; parallel GPIO is reserved for high-frame-rate display data or wide ADC sample buses.

Compare Protocol

| Metric | UART | I²C | SPI | 8-bit GPIO |

|---|---|---|---|---|

| Lines | 2 | 2 | 4 | 8+ |

| Master-slave | Peer-to-peer | Multi-master | Single master | N/A |

| Clocked? | No | Yes | Yes | Yes |

| Speed cap | 25Mbps | 5Mbps | 100Mbps | 400Mbps on-board |

| Distinct advantage | Simplicity | Addressable bus | Throughput | Zero protocol |

TFT panel integration

My team’s wearable display drove 262k-color pixels over a 16-bit parallel RGB bus at 60fps because SPI’s 36MHz ceiling could not feed 1.2Mb frame data without tearing.

How Do You Make the Right Choice for Your Project?

Choosing means balancing five levers: distance, bandwidth, latency, pin count, and power.

| Decision Lever | Serial Favored If | Parallel Favored If |

|---|---|---|

| Cable length | >30cm | 1.6Gbps synchronous |

| Acceptable latency | >100ns |

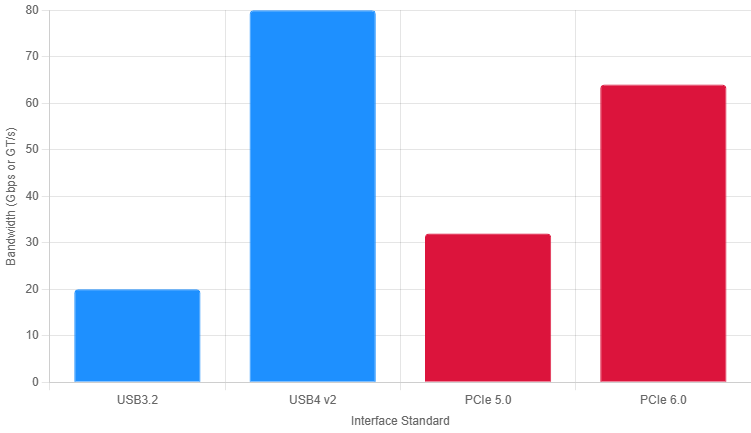

USB4 carries up to 80Gbps over two differential pairs, multiplexing DisplayPort and PCIe tunnels through packetized fabric. PCIe 6.0 reaches 64GT/s per lane—256GB/s on x16—using PAM4 signaling plus lightweight FEC to tame error rate.

These serial standards push aggregated speeds so high that parallel buses become niche, confined mostly to on-die or short memory channels.

| Standard | Raw Data Rate | Modulation | Key Innovation |

|---|---|---|---|

| USB3.2 | 20Gbps | NRZ | Dual-lane, dual-simplex |

| USB4 v2 | 80Gbps | PAM3/4 hybrid | Lane bonding, active retimers |

| PCIe 5.0 | 32GT/s | NRZ | Dual domains per link |

| PCIe 6.0 | 64GT/s | PAM4 | Flit-based FEC |

Impact on embedded design

- PHY IP for PCIe 6.0 still fits mid-range FPGAs, making 64GT/s accessible to startups within three years.

- USB4’s mandatory PD handshake simplifies power + data harness for portable medical devices, replacing parallel LVDS + DC barrel in one stroke.

Conclusion

Serial owns distance and evolution; parallel still rules tight, low-latency domains. Match your bus to your bottleneck, and let tomorrow’s serial standards carry the rest.

Related Articles:

How do timing controllers (TCON) synchronize image data in LCDs?

How Do You Choose the Best Microcontroller or Processor for Your LCD Module Project?

How is Waterproof Touch Functionality Achieved in LCD Devices?

What’s the Key Difference Between DVI-I and DVI-D Connectors?

Comprehensive Guide to eDash Mini B Display Connector Pinout

FAQ

Can Serial Communication Handle High-Resolution Displays?

Serial can handle high-resolution displays with modern standards like USB4. It offers sufficient speed and reliability for most modern LCD applications.

Is Parallel Communication Obsolete Due to New Standards?

Parallel is not obsolete but less common. It remains useful for short-distance, high-bandwidth tasks where legacy systems or specific hardware require it.

How Does Power Consumption Compare Between Serial and Parallel?

Serial typically consumes less power due to fewer pins and simpler wiring. Parallel’s multiple lines increase power usage, especially in embedded systems.

What If My Project Needs Both Speed and Long-Distance Transmission?

Modern serial standards like USB4 provide high speed over longer distances. They balance performance and reliability, often eliminating the need for parallel.

Are There Compatibility Issues When Switching Between Serial and Parallel?

Switching may require hardware redesign due to different pin counts and protocols. Always verify compatibility with your microcontroller and display requirements.